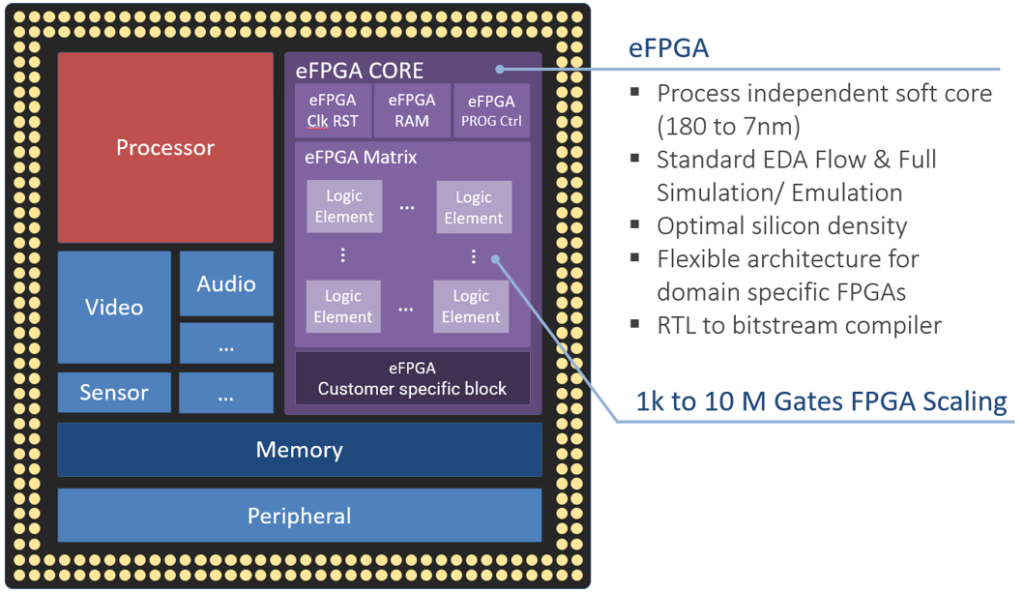

ADICSYS stands at the crossroads of ASIC design and FPGA. The company is built on more than ten years of experience in custom FPGA and embedded FPGA, or eFPGA, projects as well as leading edge semi-conductor products. ADICSYS designs and licenses soft eFPGA IP (standard cell based) for ASICs and SOCs. These embedded FPGAs are technology independent and fully integrated into standard RTL design flows

▪ Independent and distributable

▪ Embeddable in final application

Programmable IPs in our catalog:

§ Immediate access – Download efpga IP datasheet

Customized programmable IPs:

§ Dimensions and aspect ratio

§ Architecture parameters (LUT count and style, routing density…)

§ Customization for special constraints (area, performance, power)

§ Customization for special design types or use case

Verilog programmable IP comprising:

§ Synthesizable RTL – Constraint files

§ ADICSYS compilation software: Acompile

§ Bitstream loader & Test program (BIST)

Possibility to deliver a hard block (GDSII, OpenAccess, Milkyway) for a given design kit.

Personalized integration into the customers’ project based on specific constraints.

Synthesizable Programmable Core (SPC) is a soft FPGA IP for ASICs, SOCs and silicon IPs in general.

The great incentive to implement the Synthesizable Programmable Core lies in the reduction of risks associated with errors, specification changes and early adopters’ challenges. The development and verification time for critical blocks can be minimized while bring-up and debugging capabilities are enhanced.

In today’s complex systems, customizable logic can reveal itself as a key element for end user applications: pin swapping, prototype and test chip, different configuration of co-processing, post silicon debug …

SPC advantages and benefits

RTL design cycle relief

Works as for stand-alone FPGAs: correct or modify a circuit after production and in the field when a system is in service. Reduce time to market by reduce design (verification) time. Reduce risks of bugs, offers to implement workarounds or extra guaranties.

ASIC extended life

Focus on the ASIC

• No constraint for the ASIC design flow

• Accepts the induced limitations (area, circuit type)

• Access to: Simulation, Synthesis, Back end, Test (…)

• Transparent models and verification

• Reduction of cost/delay of the design phase, NRE are reduced

• Flexibility and ease to adapt to special programmable requests

Portability

Total flexibility

EASii IC rassemble une communauté de spécialistes en micro-électronique passionnée par leur métier et par les nouvelles technologies. Nous mettons en œuvre nos savoir-faire au service de nos clients pour les aider à relever les défis.