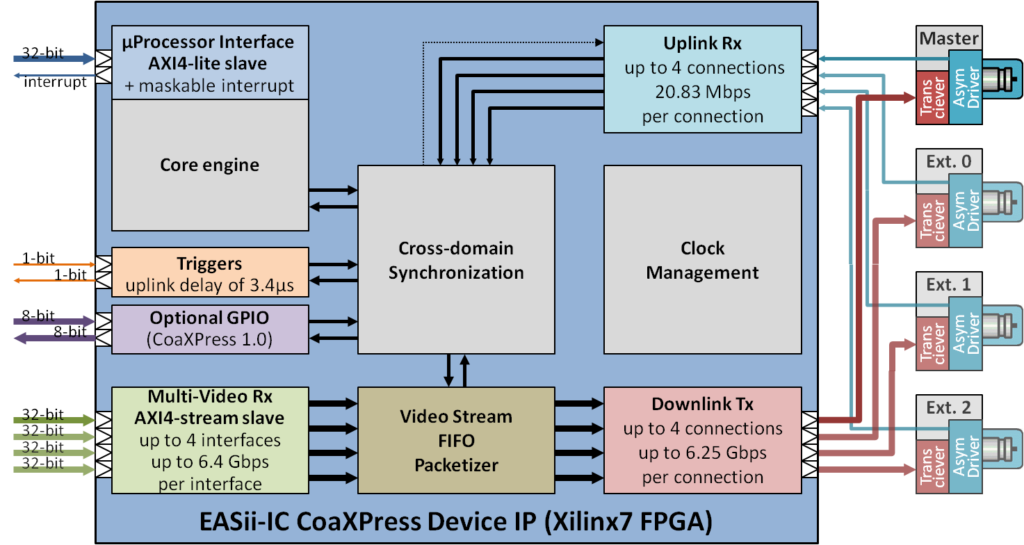

IP CXP Device

v1.1.1

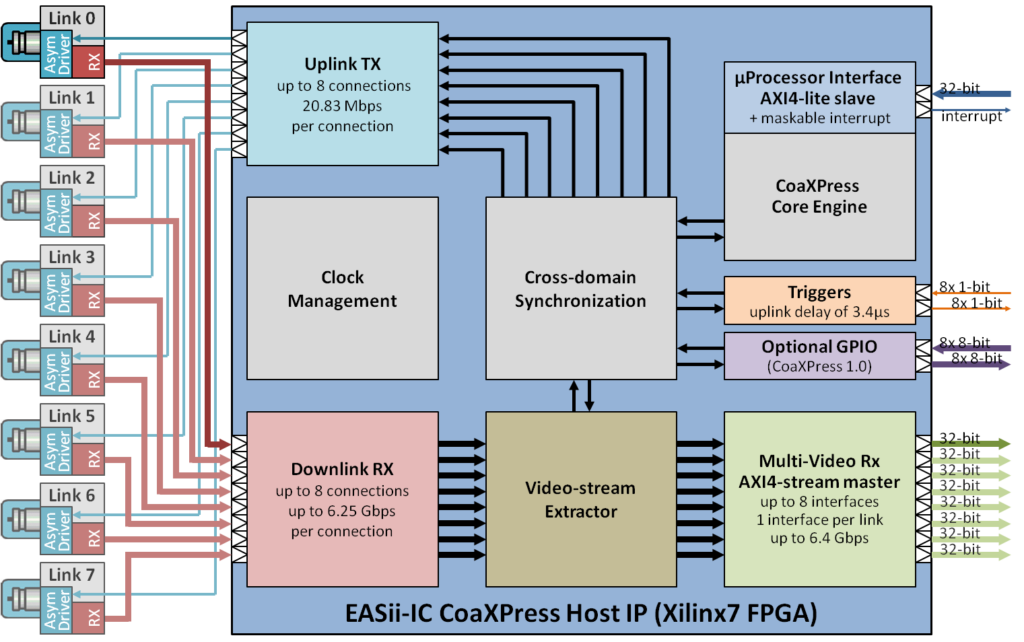

IP CXP Host

v1.1.1

IP CXP Device

v2.0

IP CXP Host

v2.0

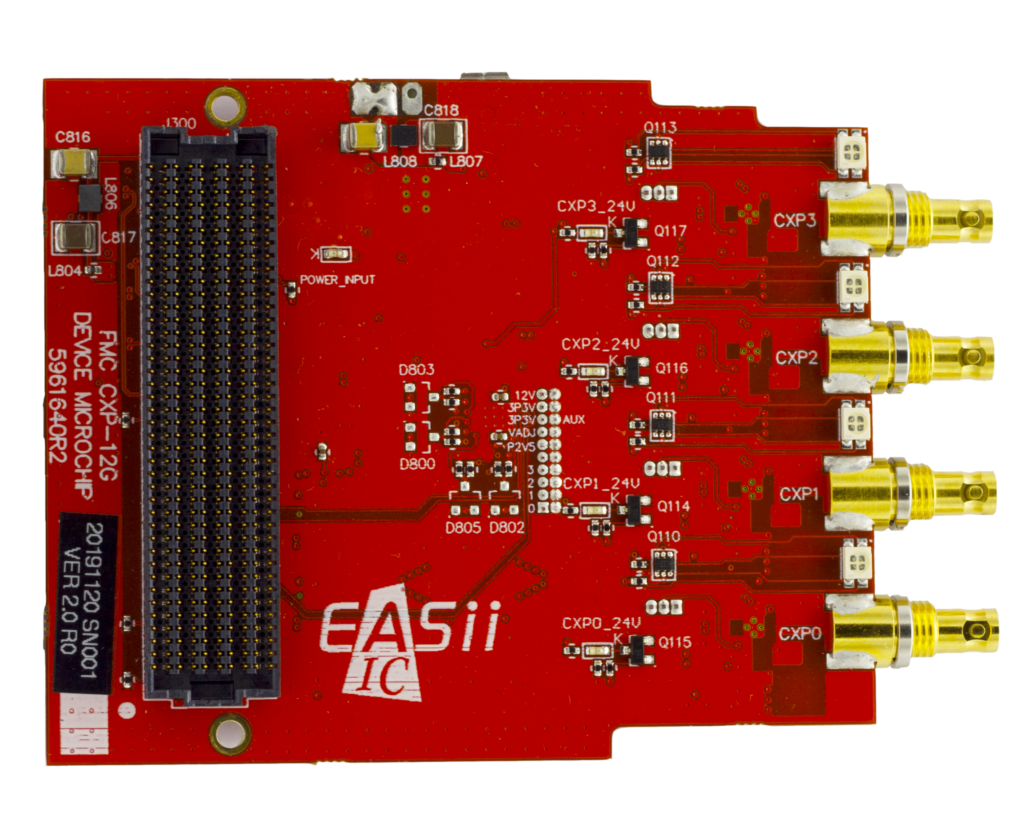

Board CXP Device

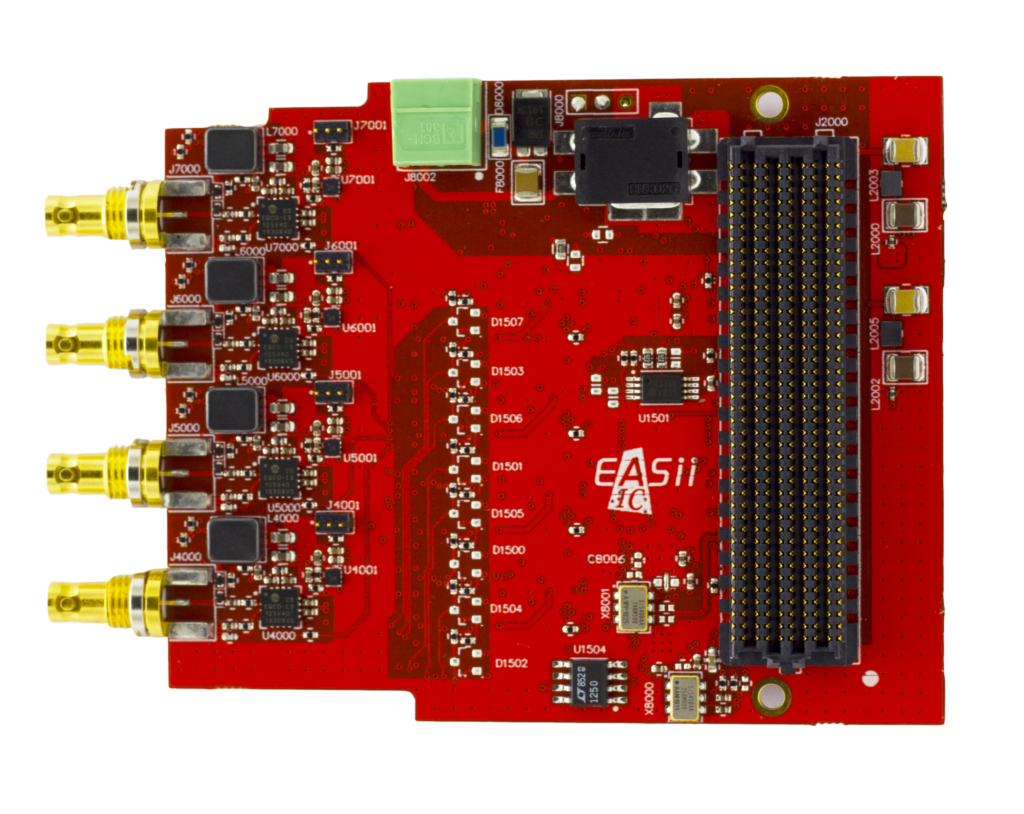

Board CXP Host

EASii IC a développé des IPs CoaXPress pour répondre à une demande interne de conception de caméras et d’enregistreurs intégrant une interface haut débit. Les IPs ont été testés et déployés sur un grand nombre de systèmes pour différentes applications et EASii IC a décidé de les proposer à ses clients pour leurs développements.

Nous avons réalisé le développement en utilisant les mêmes standards de qualité, telle que la méthodologie UVM, que pour les développements de circuits intégrés complexes (System-on-Chip). Ainsi ces blocs IP ont pu être intégrés en 1

première monte dans des produits pour le domaine aéronautique.

D’autre part, depuis quelques années, EASii IC est certifiée ISO9001 et EN9100.

EASii IC peut vous accompagner dans la réalisation de votre projet en prenant en charge le développement de systèmes électroniques et de logiciel bas niveau associés aux IP CXP. Le Centre de Design dispose d’une forte expérience en développement de cartes électroniques numériques, analogiques et RF. L’équipe CDE ( Centre de Design Electronique) dispose par ailleurs d’une grande expertise en FPGA (Centre d’excellence Xilinx/Altera/MicroSemi) ainsi que des capacités pour le développement du logiciel embarqué.

Depuis 2018, notre équipe du CDE contribue au développement du standard et fait désormais partie des principaux acteurs depuis la version 2.0.

CoaXPress (CXP) est la principale norme mondiale pour l’imagerie à haute vitesse dans les applications d’imagerie professionnelles et industrielles telles que la vision industrielle, l’imagerie médicale, les sciences de la vie, la diffusion et la défense.

CoaXPress combine la simplicité traditionnelle du câble coaxial avec la technologie de pointe de données série à haute vitesse.

La combinaison de ces deux caractéristiques – câble coaxial et vitesse « express » – fournit une solution hautement souhaitable pour l’imagerie et la transmission de données à haute vitesse.

La norme est hébergée par JIIA (Japan Industrial Imaging Association) avec des groupes de travail d’entreprises du monde entier.

Il s’agit d’une solution haut débit à faible coût pour l’interfaçage avec des périphériques d’acquisition vidéo distants via des câbles coaxiaux RG59 et RG6. Il permet la connexion à chaud des périphériques et leur alimentation à distance en 24V jusqu’à 13 watts par câble.

Un hôte (« host ») peut prendre en charge plusieurs caméras avec un très grand nombre de formats vidéos. Le standard CoaXPress définit une implémentation du standard GenICam, offrant ainsi une interface logicielle unifiée pour tous types de caméras, quel que soit leurs interfaces.

Les flux vidéos, au nombre de 256 max, sont envoyés par un périphérique (« device ») vers l’hôte à un débit descendant configurable de 1,25 Gbps à 12,5 Gbps par câble en se basant sur un codage 8b/10b. Chaque périphérique peut disposer d’une ou plusieurs connexions câble ; un périphérique avec 8 connexions permet d’atteindre un débit total de 100 Gbps.

Les périphériques sont pilotés depuis l’hôte via la liaison ascendante à un débit configurable de 20,833 Mbps à 41,667 Mbps. Le standard offre également un mécanisme de déclenchement à distance, bidirectionnel entre les périphériques et l’hôte, de faible latence et de haute précision.

Les IPs que nous avons développés sont déjà intégrés dans des équipements qui sont en première monte dans des systèmes industriels et aéronautiques.

Nous avons la maîtrise de l’ensemble des technologies et du savoir faire qui sont indispensables à la conception et au développement de solutions à base de CoaXPress.

C’est ce qui permet aujourd’hui à EASii IC d’être une des rares sociétés à proposer une gamme de caméras et de serveurs développés sur mesure pour les besoins spécifiques de ses clients.

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

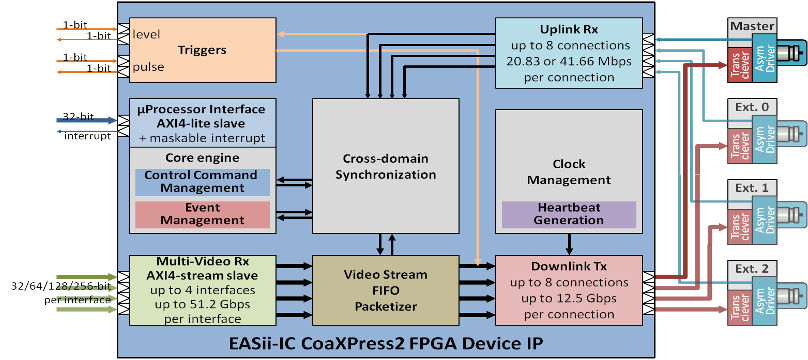

CoaXPress 2.0 Device IP from EASii-IC enables the transmission of up to 256 video streams from multiple cameras over 1 to 8 coaxial cable connections operating at 1.25 Gbps to 12.5 Gbps, delivering a total transfer rate of up to 100 Gbps.

Hardware link state, bootstrap register and discovery management fully compatible with CoaXPress 2.0 and 1.1.1

Dynamic link reconfiguration while operating supported

Up to 256 independent video-streams at any downconnection bit-rate, with programmable IDs

Extensive interoperability and UVM verification

300+ tests with randomization, plugfest certified

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up to 100 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to 100 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

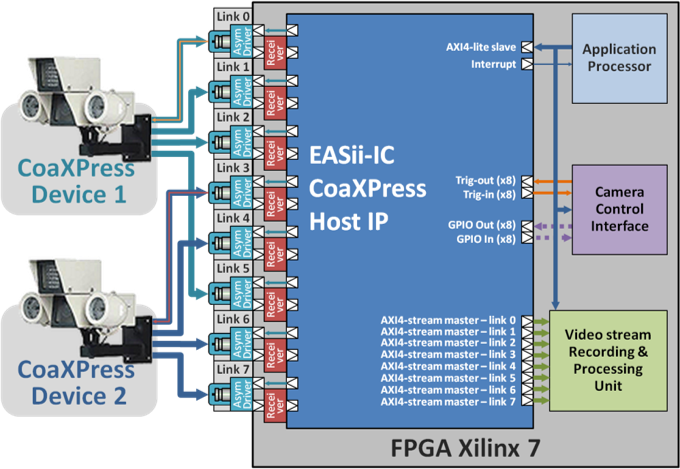

CoaXPress 2.0 Host IP from EASii-IC enables the reception of 256 video streams at up to 100 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate. Dynamic device link reconfiguration while operating supported.

Up to 8 coaxial connections any arbitrary connection topology of 1 to 8 devices, each of 1 to 8 connections, for a total of up to 8 cables, each device at any independent standard downconnection bit-rate from 1.25 Gbps to 12.5 Gbps;

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up

to 100 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to 100 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

CoaXPress Host IP from EASii-IC enables the reception of 256 video streams at up to 50 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate.

Dynamic device link reconfiguration while operating supported

Hardware device discovery management fully compatible with CoaXPress 1.1.1 and 1.1 devices

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up to 50 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to 50 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

CoaXPress Host IP from EASii-IC enables the reception of 256 video streams at up to 50 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate.

Dynamic device link reconfiguration while operating supported

Hardware device discovery management fully compatible with CoaXPress 1.1.1 and 1.1 devices

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up

to 50 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to 50 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

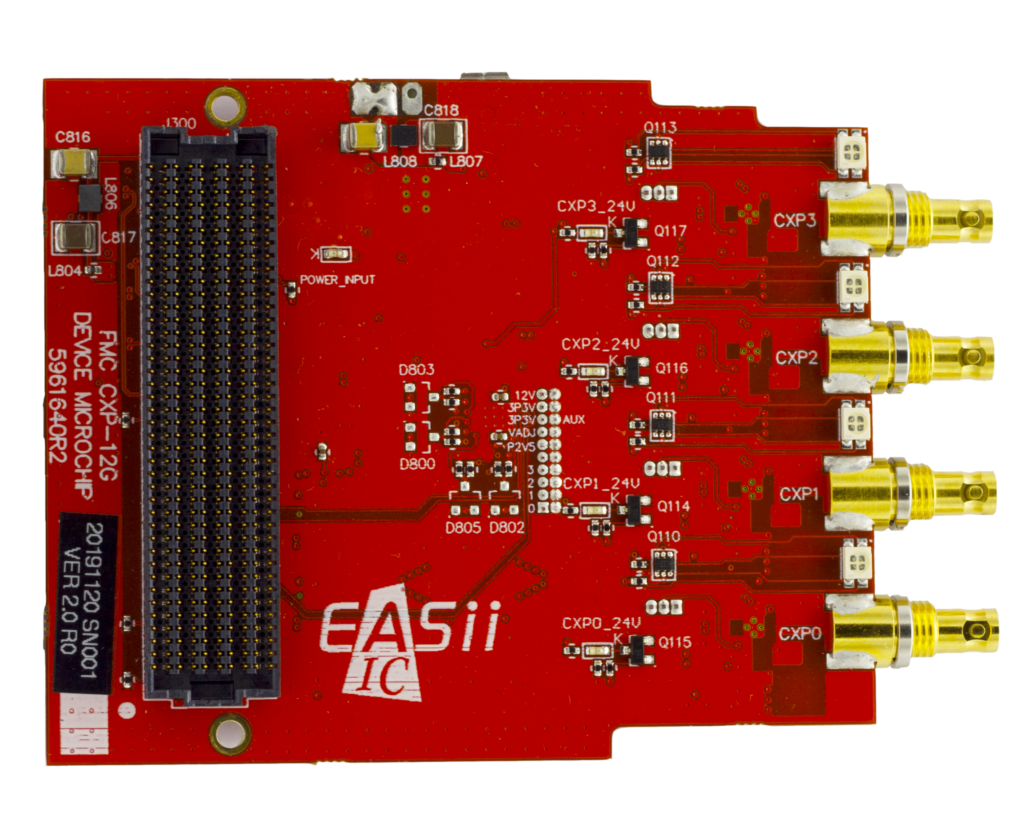

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

The EASii-IC CoaXPress Device FMC Board is a 4-connection, stackable to 8-connection, single-width board, com-patible with the ANSI/VITA 57.1 FPGA Mezzanine Card (FMC) standard. Each board provides 4 device connections compliant with the CoaXPress 2.0 and 1.1.1 standards operating at up to 12.5 Gbps. Two boards can be stacked to provide up to 8 connections.

4 coaxial 75 ohms HD-BNC connectors providing 4 CoaXPress device connections at operating bit-rates from 1.25 Gbps to 12.5 Gbps

Stackable to provide up to 8 device connections through a 2nd Samtec FMC HPC connector

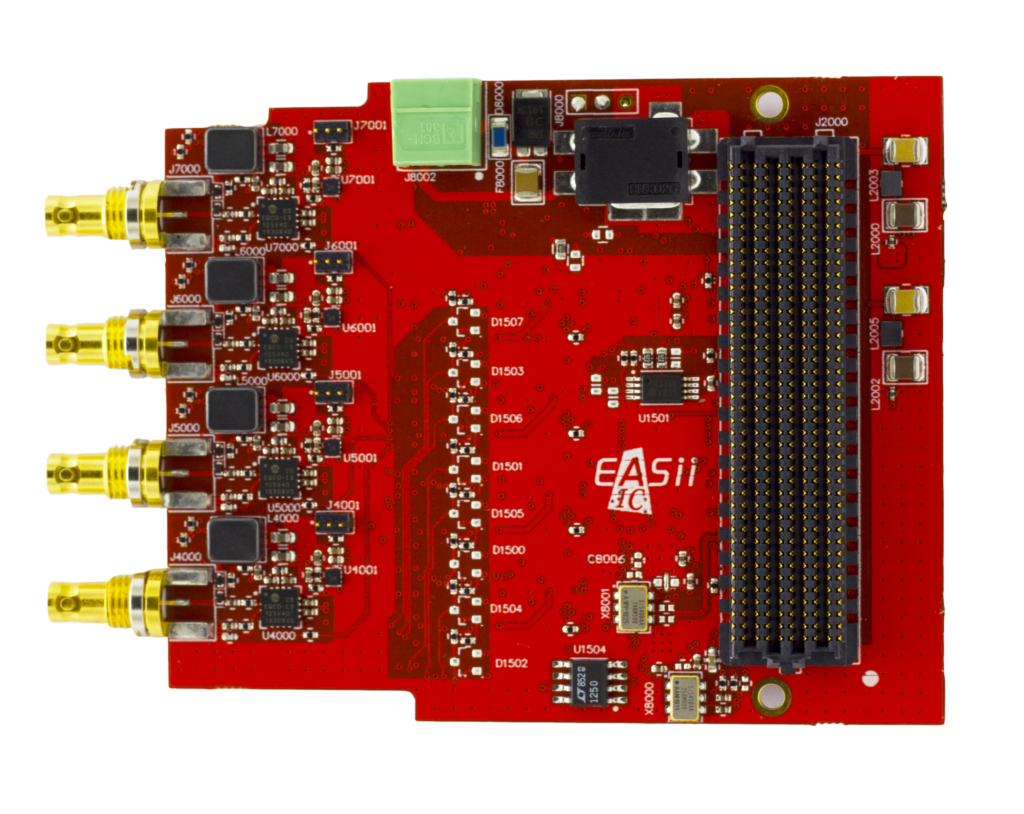

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

The EASii-IC CoaXPress Host FMC Board is a 4-connection, stackable to 8-connection, single-width board, compatible with the ANSI/VITA 57.1 FPGA Mezzanine Card (FMC) standard. Each board provides 4 host ports compliant with the CoaXPress 2.0 and 1.1.1 standards operating at up to 12.5 Gbps. Two boards can be stacked to provide up to 8 ports.

4 coaxial 75 ohms HD-BNC connectors providing 4 CoaXPress device connections at operating bit-rates from 1.25 Gbps to 12.5 Gbps

Stackable to provide up to 8 host ports through a 2nd Samtec FMC HPC connector

6.25 Gbps per link

30m (6,25Gbps/lane)

30m (6,25Gbps/lane)

30m (6,25Gbps/lane)

30m (6,25Gbps/lane)