IP CXP Device

v1.1.1

IP CXP Host

v1.1.1

IP CXP Device

v2.0

IP CXP Host

v2.0

Board CXP Device

Board CXP Host

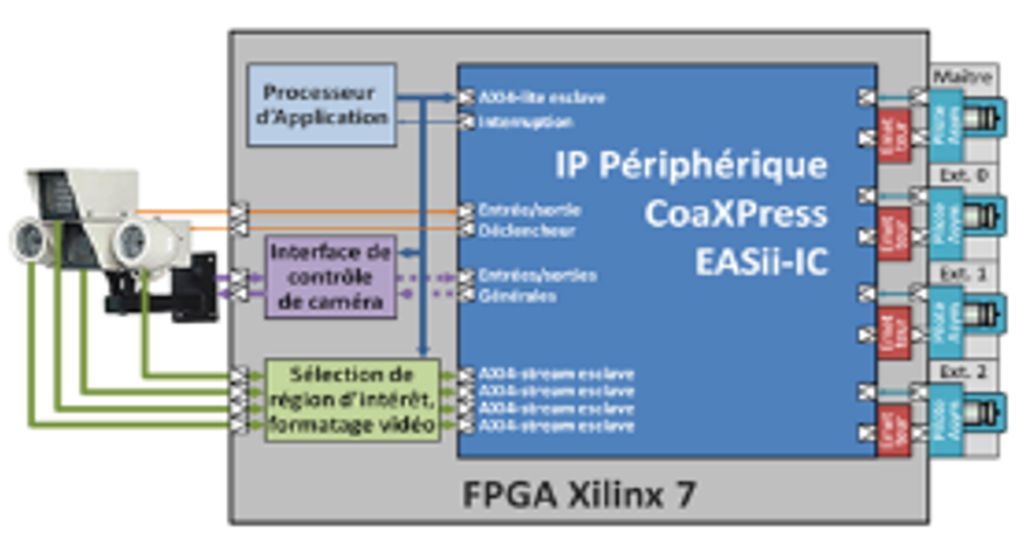

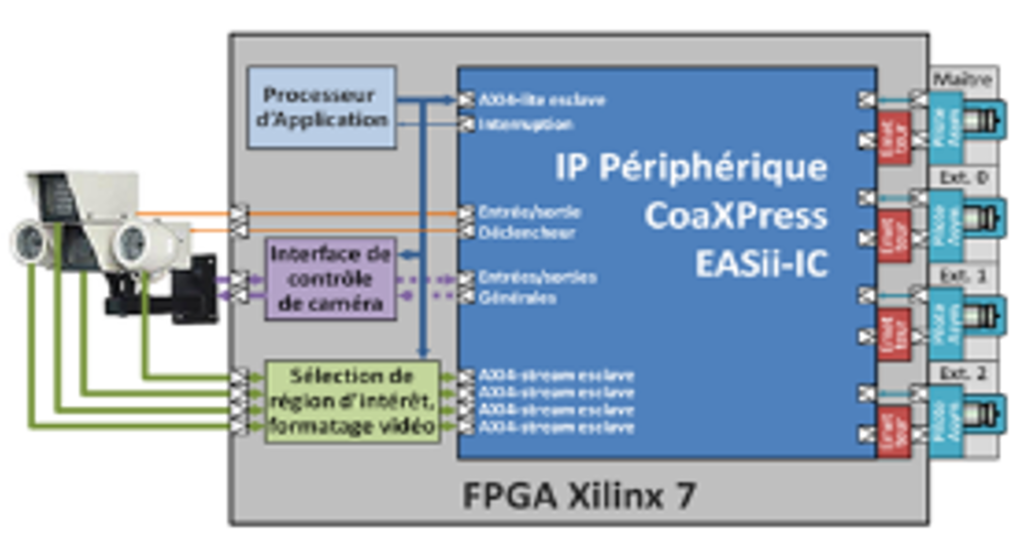

EASii IC has developed CoaXPress IPs to meet an internal demand for the design of cameras and recorders integrating a high speed interface. The IPs have been tested and deployed on a large number of systems for different applications and EASii IC has decided to offer them to its customers for their developments.

We carried out the development using the same quality standards, such as the UVM methodology, as for the development of complex integrated circuits (System-on-Chip). Thus, these IP blocks could be integrated in the original equipment in products for the aeronautical field.

On the other hand, in recent years, EASii IC has been ISO9001 and EN9100 certified.

EASii IC can support you in the realization of your project by supporting the development of electronic systems and low level software associated with IP CXP. The Design Center has extensive experience in the development of digital, analog and RF electronic cards. The CdD team also has great expertise in FPGA (Xilinx / Altera / MicroSemi Center of Excellence) as well as capabilities for the development of embedded software.

Since 2018, our CdD team has contributed to the development of the standard and is now one of the main players since version 2.0.

CoaXPress (CXP) is the leading global standard for high speed imaging in professional and industrial imaging applications such as machine vision, medical imaging, life sciences, broadcast and defense.

CoaXPress combines the traditional simplicity of coaxial cable with advanced high-speed serial data technology.

The combination of these two characteristics – coaxial cable and “express” speed – provides a highly desirable solution for high speed imaging and data transmission.

The standard is hosted by JIIA (Japan Industrial Imaging Association) with working groups from companies around the world.

It is a low-cost, high-speed solution for interfacing with remote video capture devices via RG59 and RG6 coaxial cables. It allows the hot-plugging of peripherals and their remote power supply in 24V up to 13 watts by cable.

A host can support multiple cameras with a very large number of video formats. The CoaXPress standard defines an implementation of the GenICam standard, thus offering a unified software interface for all types of cameras, whatever their interfaces.

Video streams, up to 256 in number, are sent by a device to the host at a configurable downstream rate of 1.25 Gbps to 12.5 Gbps by cable based on 8b / 10b encoding . Each device can have one or more cable connections; a device with 8 connections achieves a total speed of 100 Gbps.

The devices are driven from the host through the uplink at a configurable rate of 20.833 Mbps to 41.667 Mbps. The standard also offers a remote, bidirectional trigger mechanism between devices and the host, with low latency and high precision.

The IPs that we have developed are already integrated into equipment which is first-stage in industrial and aeronautical systems.

We have mastery of all the technologies and know-how that are essential for the design and development of CoaXPress-based solutions.

This is what allows EASii IC today to be one of the rare companies to offer a range of cameras and servers developed to measure for the specific needs of its customers.

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

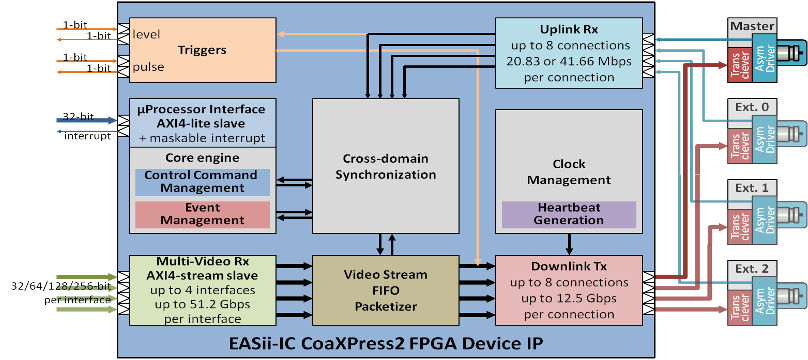

CoaXPress 2.0 Device IP from EASii-IC enables the transmission of up to 256 video streams from multiple cameras over 1 to 8 coaxial cable connections operating at 1.25 Gbps to 12.5 Gbps, delivering a total transfer rate of up to 100 Gbps.

Hardware link state, bootstrap register and discovery management fully compatible with CoaXPress 2.0 and 1.1.1

Dynamic link reconfiguration while operating supported

Up to 256 independent video-streams at any downconnection bit-rate, with programmable IDs

Extensive interoperability and UVM verification

300+ tests with randomization, plugfest certified

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up to 100 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to

100 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

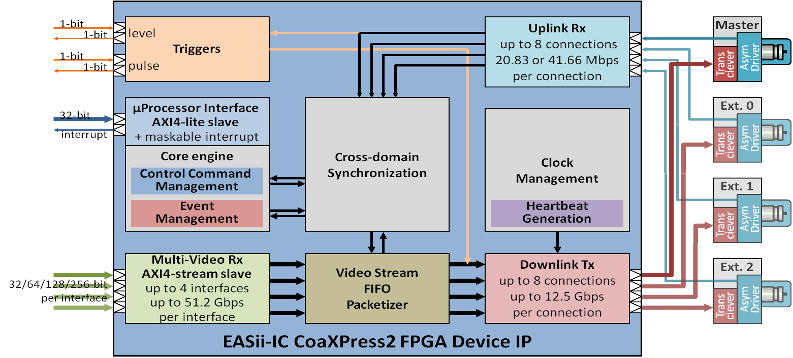

CoaXPress 2.0 Host IP from EASii-IC enables the reception of 256 video streams at up to 100 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate. Dynamic device link reconfiguration while operating supported.

Up to 8 coaxial connections any arbitrary connection topology of 1 to 8 devices, each of 1 to 8 connections, for a total of up to 8 cables, each device at any independent standard downconnection bit-rate from 1.25 Gbps to 12.5 Gbps;

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1 or CoaXPress 2.0

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up

to 100 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to

100 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

CoaXPress Host IP from EASii-IC enables the reception of 256 video streams at up to 50 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate.

Dynamic device link reconfiguration while operating supported

Hardware device discovery management fully compatible with CoaXPress 1.1.1 and 1.1 devices

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up to

50 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to

50 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

CoaXPress Host IP from EASii-IC enables the reception of 256 video streams at up to 50 Gbps through 8 coaxial cable connections. The EASii-IC Host IP supports all interconnection topologies 1 to 8 CoaXPress devices, of devices of 1 to 8 connections, for a total of 8 connections, at any standard bit-rate.

Dynamic device link reconfiguration while operating supported

Hardware device discovery management fully compatible with CoaXPress 1.1.1 and 1.1 devices

Hardware-based video-stream management automated error detection and recovery at image-level stream status and format monitoring interface

EASii IC provides a full CoaXPress Design environment including:

– FPGA CoaXPress Device IP core for CoaXPress 1.1.1

– FPGA CoaXPress Host IP core for CoaXPress 1.1.1

– FMC-CXP 4 x CXP12 Device daughter board that can be stacked for up

to 50 Gbps bandwidth

– FMC-CXP 4 x CXP12 Host daughter board that can be stacked for up to

50 Gbps bandwidth

– Full CoaXPress Host and Device Reference design

– IP Integration and Board Design support

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

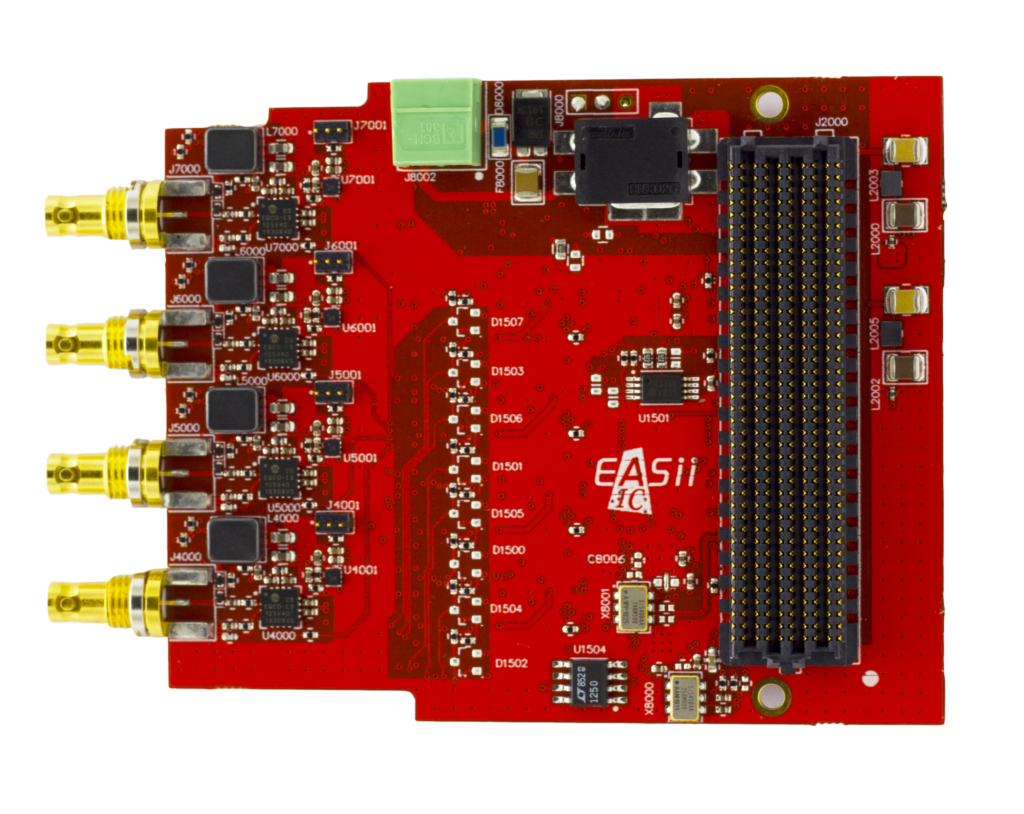

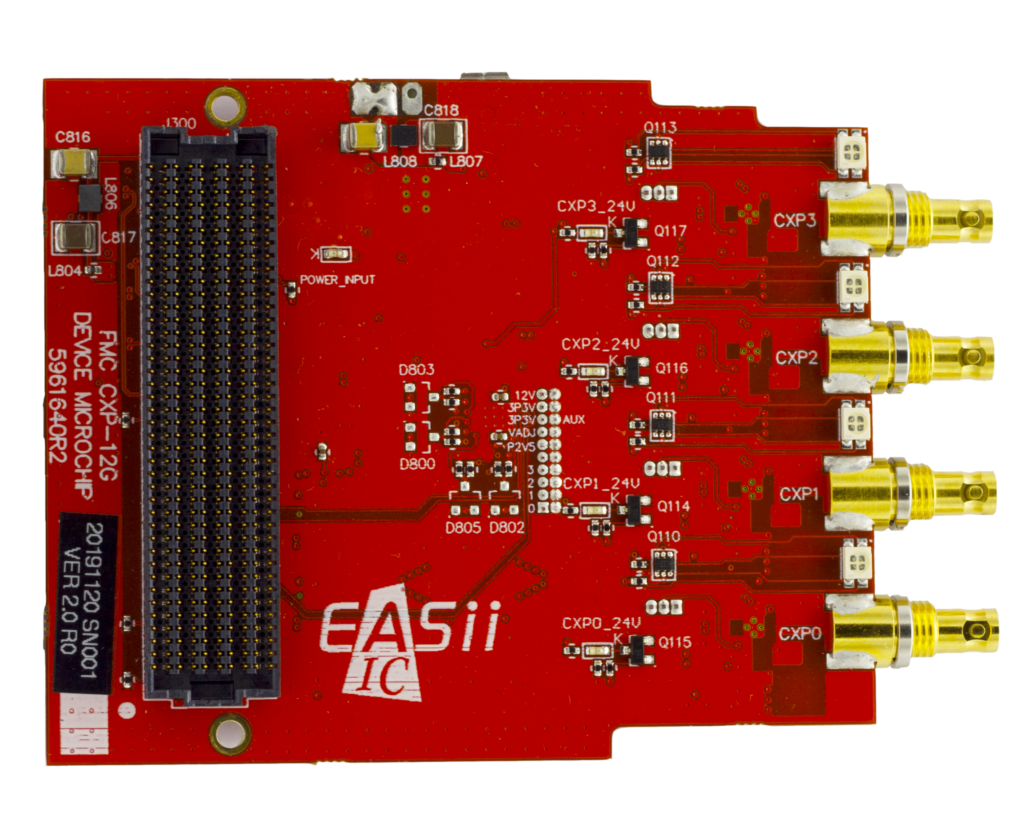

The EASii-IC CoaXPress Device FMC Board is a 4-connection, stackable to 8-connection, single-width board, com-patible with the ANSI / VITA 57.1 FPGA Mezzanine Card (FMC) standard. Each board provides 4 device connections compliant with the CoaXPress 2.0 and 1.1.1 standards operating at up to 12.5 Gbps. Two boards can be stacked to provide up to 8 connections.

4 coaxial 75 ohms HD-BNC connectors providing 4 CoaXPress device connections at operating bit-rates from 1.25 Gbps to 12.5 Gbps

Stackable to provide up to 8 device connections through a 2nd Samtec FMC HPC connector

JIIA CXP-001-2019 CoaXPress 2.0 compliant & JIIA CXP-001-2015 CoaXPress 1.1.1 compliant

The EASii-IC CoaXPress Host FMC Board is a 4-connection, stackable to 8-connection, single-width board, compatible with the ANSI / VITA 57.1 FPGA Mezzanine Card (FMC) standard. Each board provides 4 host ports compliant with the CoaXPress 2.0 and 1.1.1 standards operating at up to 12.5 Gbps. Two boards can be stacked to provide up to 8 ports.

4 coaxial 75 ohms HD-BNC connectors providing 4 CoaXPress device connections at operating bit-rates from 1.25 Gbps to 12.5 Gbps

Stackable to provide up to 8 host ports through a 2nd Samtec FMC HPC connector